# The COTS Technology Authority EMBEDDED SYSTEMS VOLUME 2 NUMBER 3 FALL 2006

IN THIS ISSUE:

#### Chris A. Ciufo

Intel Xeon UIV vs. PowerPC

#### **Jerry Gipper**

"Keeping fast company"

#### **Special Guest**

Jim Turley asks: "Inventor or Patent Troll?"

# Keep your SPARC supply lines open.

#### USP Ile™ VMEbus Computer

650-MHz UltraSPARC® IIi+ CPUs 4GB SDRAM

Optional TGA3D+™ and TGA-100™ graphics support **Gigabit Ethernet**

PCI expansion to four slots

Four serial ports

VME Interface - VME64X via Tundra Universe II

PS/2 or USB keyboard/mouse Solaris™ 8/9/10 Support

USP IIIi™ VMEbus Computer

4GB 266DDR SDRAM per CPU, 8GB total Optional TGA3D+ and TGA-100 graphics Gigabit Ethernet port One 64-bit/66-MHz PMC slot Up to four PMC expansion slots **Dual FC-AL/SCSI ports** Additional VME-backplane access Up to 30G shock Solaris OS Support

Do your mission critical applications depend on SPARC/ Solaris solutions? Many suppliers are ending their support for SPARC-based single board computers. Not Themis. Themis is committed to providing its customers and industry with high performance UltraSPARC VMEbus single board computers.

Stock up on

Themis has solutions. We are committed to providing you with the industry's widest breadth of high performance UltraSPARC-based VME single board computers. To support thousands of Solaris platform solutions for the most demanding mission critical applications.

Don't be forced into changing your computing platform today. Extend the life of your system and gain control over your program lifecycle and budget with Themis SPARC solutions.

Themis is keeping the SPARC supply lines open so call Themis today.

www.themis.com (510) 252-0870

Transformational.

RSC# 2 @www.mil-embedded.com/rsc

Back in 1981, while people were busy spinning on their heads, Motorola launched VME and left the embedded computing competition flat on its back.

# Now, 25 years later, Arrow Electronics and Motorola are defining the new era in embedded computing with MicroTCA™ solutions.

**MicroTCA communications servers** use a revolutionary system architecture to meet the military's budget requirements and work within an open architecture computing environment. Motorola is recognized for its key role in ushering in this innovative technology. Backed by Arrow's broad line card, technical expertise, services, outstanding integration capabilities, and supply chain solutions, MicroTCA technology reduces the time required to deploy and refresh systems.

**WDW**

Offering the economies of commercial off-the-shelf products and the flexibility of custom solutions, MicroTCA technology co-exists with VME and extends the life of previous investments through:

- Adherence to standards-based open architecture systems requirements

- Very compact form factor

- Superior chassis flexibility

- Compute density and scalability

- Hot-swappable Advanced Mezzanine Cards

- A common base platform and associated cost savings

#### Development units available.

Call 888-427-2250 or visit www.arrownac.com/NotAPassingTrend to learn why MicroTCA technology is destined to influence embedded computing for a long time to come. Quantities are limited, so call now!

©2006 Arrow Electronics, Inc. Arrow and the Arrow logo are registered trademarks; MOTOROLA and the Stylized M Logo are registered in the US Patent & Trademark Office. PICMG and the PICMG logo are registered trademarks, and MicroTCA is a trademark of the PCI Industrial Computer Manufacturers Group.

VOLUME 2 NUMBER 3

FALL 2006

www.mil-embedded.com

#### DEPARTMENTS

#### **Industry Analysis**

8 **Keeping fast company** By Jerry Gipper

10 Brilliant inventor or patent troll? By Jim Turley, Patriot Scientific

#### **Departments**

**Editor's Choice Products** 42

48 **New Products** By Sharon Schnakenburg

#### **Crosshairs Editorial**

54 Intel Xeons encroach on PowerPC's territory By Chris A. Ciufo

Advertiser Index 6

#### -CASTS

"Tackling FPGA design challenges for embedded systems," presented by Pentek November 30, 2 p.m. EDT

www.opensystems-publishing.com/ecast

"Optimizing DSP algorithms for FPGA implementation," presented by Synplicity

December 6, 2 p.m. EDT www.opensystems-publishing.com/ecast

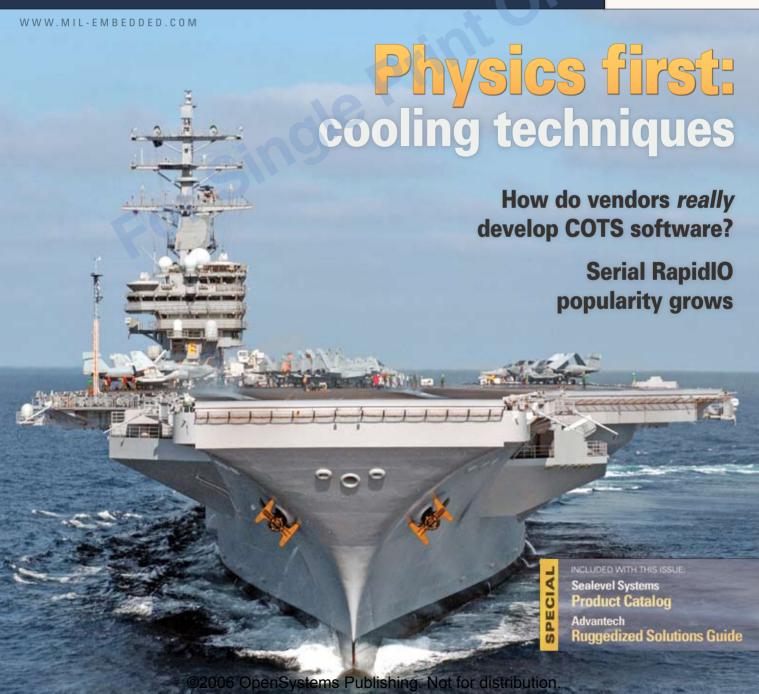

The new carrier USS Ronald Reagan (CNV 76) conducts operations off the coast of southern California. You can bet the ship is loaded with COTS hardware and software, from the flight deck bridge to the weapons ops center to the avionics suites controlling her aircraft in flight. But how is COTS software developed? How do designers keep high-performance electronics cool? See articles starting on pages 12 and 38.

(Image courtesy of U.S. Navy, www.news.navy.mil. Photo taken by Mass Communication Specialist 3rd Class Sarah Foster.)

© Military Embedded Systems

All registered brands and trademarks within Military Embedded Systems magazine are the property of their respective owners.

Published by:

#### 4 / FALL 2006

HARDWARE: Desert design techniques: Physics first

Improved cooling technologies for both power-supply and motor-drive military applications

By Ralph Remsburg, Amulaire Thermal Technology

Adaptive meshing helps Army develop Future Combat 16 Systems: CFD software models muzzle recoil

By Jerry Fireman, representing Fluent Inc. and Benét Laboratories

ANE: Operating Systems

Using resource partitioning to build secure, survivable military systems

By Paul N. Leroux and Kerry Johnson, QNX Software Systems

**TECHNOLOGY:** System interconnects

Using your existing test and measurement platform to perform Serial RapidIO protocol analysis

By Barbara Aichinger, FuturePlus Systems

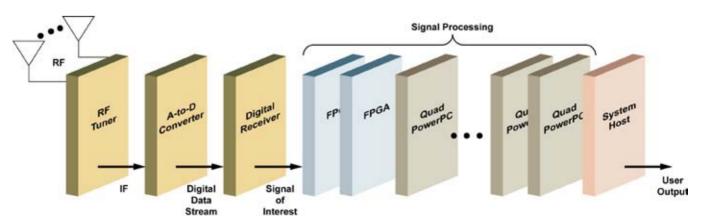

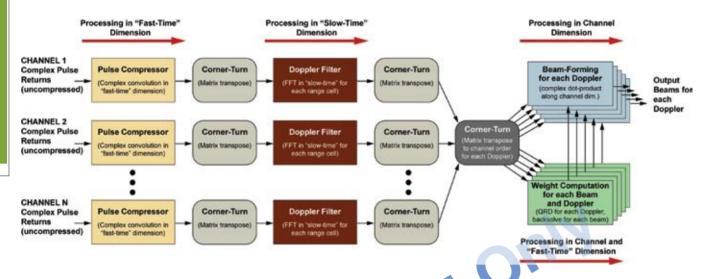

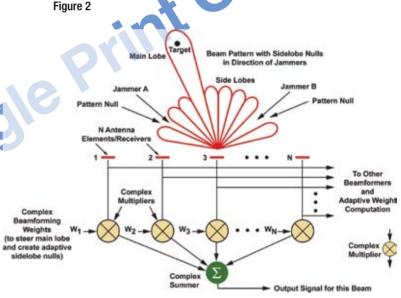

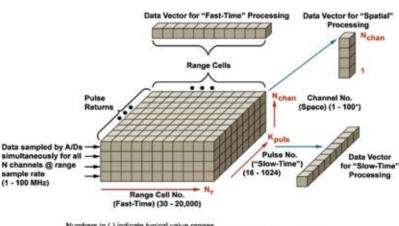

32 Multi-function radar systems for the deployed warrior using VPX-REDI and RapidIO

By James Meyer, Mercury Computer Systems, Inc.

MIL TECH TRENDS: COTS software: From concept to reality

The COTS software market doesn't run on DoD time 38 By Chris A. Ciufo

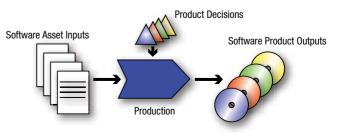

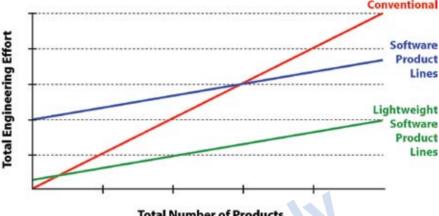

39 The emerging practice of software product line development

By Charles W. Krueger, PhD, BigLever Software, Inc.

PRODUCT GUIDE: XMC base boards, mezzanine 44 boards, and related XMC products

#### F-I ETTER

www.mil-embedded.com/eletter

SDR and JTRS: Lessons learned

Q & A with Col. Steven MacLaird, former Program Executive Director of the Joint Tactical Radio System JPO

By Chris A. Ciufo

Visit us online for the complete list of articles

#### Subscribe to the magazine or E-letter:

www.opensystems-publishing.com/subscriptions

## **Advertiser** Information

|           | mormation                                                             |

|-----------|-----------------------------------------------------------------------|

| Page/RSC# | Advertiser/Product description                                        |

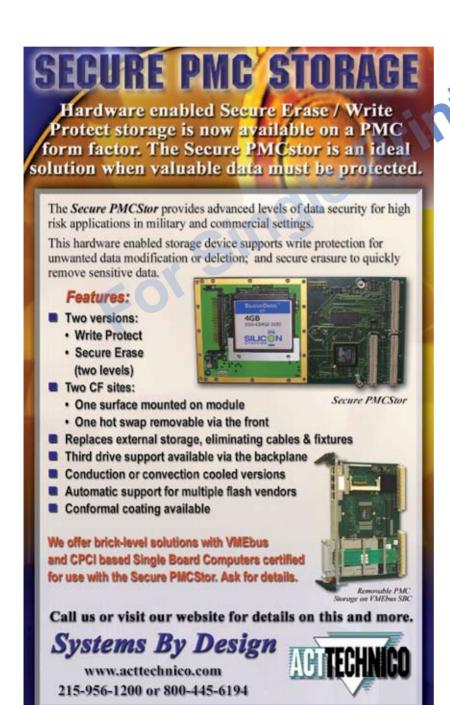

| 48        | ACT/Technico – PMC Storage                                            |

| 50        | Advantech Corporation – Stackable SBCs                                |

| 11        | Aitech Defense Systems – VMEbus and CompactPCI Products               |

| 25        | Annapolis Micro Systems – FPGA Systems                                |

| 3         | Arrow Electronics – MicroTCA Communications Servers                   |

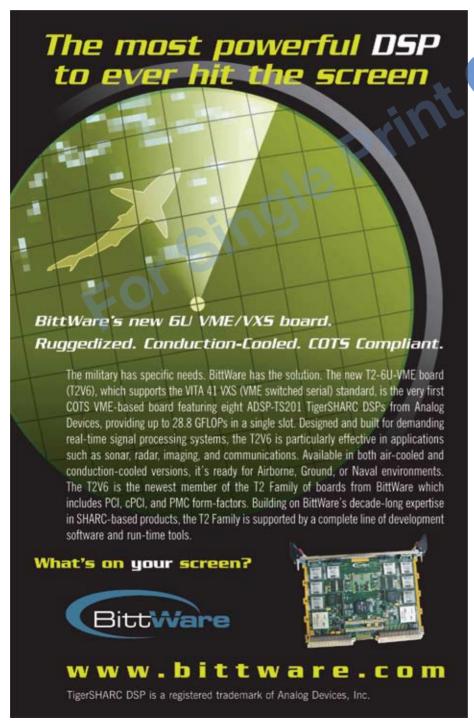

| 26        | BittWare – 6U VME/VXS Board                                           |

| 40        | Concurrent Technologies – Intel SBCs                                  |

| 56        | Curtiss Wright – VPX SBCs                                             |

| 22        | Datametrics – Ruggedized Information Technology                       |

| 31        | DIGITAL-LOGIC – MPCX48                                                |

| 49        | Embedded Planet – EP8548A Serial RapidlO AMC                          |

| 23        | Excalibur Systems – Avionics Communications                           |

| 55        | GE Fanuc Embedded Systems – Embedded Products                         |

| 35        | General Standards – High-performance Analog, Digital, and             |

|           | Serial I/O                                                            |

| 7         | Harris RF Communications – Sierra Encryption Modules                  |

| 51        | Hybricon – Liquid Cooled 100 W/Slot 1 ATR                             |

| 9         | ICS Sensor Processing – ICS-8552B and ICS-8554                        |

| 5         | Intel – Cost-Effective Solutions                                      |

| 43        | Jacyl Technology – PC/104 FPGA Circuit Boards                         |

| 37        | MPL AG – Rugged Embedded Computers                                    |

| 53        | North Atlantic Industries – Intelligent Multifunction I/O Cards       |

| 36        | Phoenix International – Data Storage Modules                          |

| 28        | RTD Embedded Technologies – HighRel PC/PCI-104 Modules                |

| 20        | and Systems                                                           |

| 33        | Schroff – Hybrid Serial Parallel Cooling                              |

| 6         | TEWS Technologies – COTS I/O Solutions                                |

| 47<br>2   | Thales – PENTXM2 Thomis Computer SPARC SPCs                           |

| 2<br>15   | Themis Computer – SPARC SBCs Tri-M Systems – Modules, Flash Solutions |

|           |                                                                       |

| 13        | Tri-M Systems – Modules, Power Supply                                 |

# litary embedded systems

AN OPENSYSTEMS PUBLICATION

#### Military and Aerospace Group

- DSP&FPGA Product Resource Guide

- DSP-FPGA com

- DSP-FPGA.com E-letter

- Military Embedded Systems

- Military Embedded Systems E-letter

- PC/104 & Small Form Factors

- PC/104 & Small Form Factors E-letter

- PC/104 & Small Form Factors Resource Guide

- VMEbus Systems

- VMEbus Systems E-letter

Group Editorial Director Chris A. Ciufo

cciufo@opensystems-publishing.com

Senior Editor (columns) Terri Thorson

tthorson@opensystems-publishing.com

Assistant Editor Sharon Schnakenburg

sschnakenburg@opensystems-publishing.com

**European Representative** Hermann Strass

hstrass@opensystems-publishing.com

Art Director Steph Sweet Senior Web Developer

Graphic Specialist David Diomede Circulation/Office Manager Phyllis Thompson

subscriptions@opensystems-publishing.com

#### OpenSystems Publishing

#### Editorial/Production office:

16872 E. Ave of the Fountains, Ste 203, Fountain Hills, AZ 85268

Website: www.opensystems-publishing.com

Publishers John Black, Michael Hopper, Wayne Kristoff

Vice President Editorial Rosemary Kristoff

#### **Communications Group**

Editorial Director Joe Pavlat

Senior Editor (columns) Terri Thorson Technology Editor Curt Schwaderer European Representative Hermann Strass

#### **Embedded and Test & Analysis Group**

Editorial Director Don Dingee Editorial Director Jerry Gipper Technical Editor Chad Lumsden Associate Editor .lennifer Hesse

European Representative Hermann Strass Special Projects Editor Bob Stasonis

#### **Reprints and PDFs**

Call the sales office: 586-415-6500

#### ISSN: Print 1557-3222

Military Embedded Systems (USPS 019-288) is published four times a year (Spring, Summer, Fall, Winter) by OpenSystems Publishing LLC, 30233 Jefferson Avenue, St. Clair Shores, MI 48082

Subscriptions are free to persons interested in the design or promotion of Military Embedded Systems. For others inside the US and Canada, subscriptions are \$28/year. For 1st class delivery outside the US and Canada, subscriptions are \$50/year (advance payment in US funds required).

Canada: Publication agreement number 40048627

Return address WDS, Station A PO Box 54, Windsor, ON N9A 615

POSTMASTER: Send address changes to Military Embedded Systems 16872 E. Ave of the Fountains, Ste 203, Fountain Hills, AZ 85268

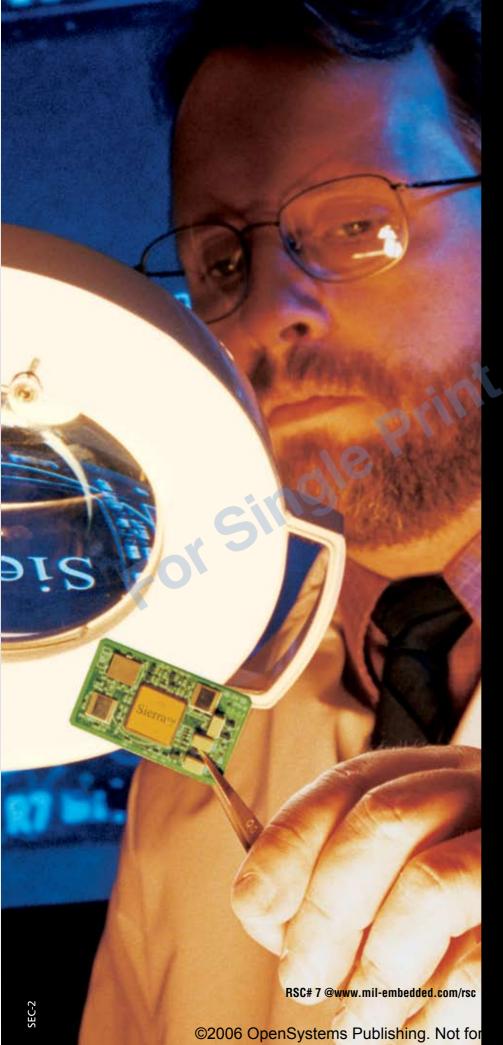

Take a closer look at your encryption.

# Are you getting the protection you need?

Members of the Sierra™ family of encryption modules are easily integrated into communications devices of all kinds. Sierra encrypts classified information, processes data at a higher speed, is extremely power efficient, and allows modules to be reprogrammed as missions change.

It's benefits like these that led the U.S. Department of Defense to select Sierra II for one of the most important communications programs in recent history. Sierra II has been chosen to encrypt 100 percent of the radios under Cluster 1 of the U.S. Joint Tactical Radio System program.

www.harris.com

RF Communications

Government

Broadcast

Microwave

*assuredcommunications*™

# **Industry Analysis**

## **Keeping fast company**

By Jerry Gipper

In the spring of 1981, I was in the final days of my preparation for entry into the real world. The computer labs at Iowa State University were my second home. My first introduction to card buses was the S-100 bus. I was attending demonstrations on emerging PC technology sponsored by Commodore and Radio Shack. I was reading *Byte* magazine when it was still in existence and less than 100 pages!

1981 was a busy year for technology. On April 12, many of us sat on the edge of our seats as we witnessed the launch of Space Shuttle Columbia. After a successful two-day mission, we also watched as it touched down on the long runway at Edwards Air Force Base. (I was in one of those ISU labs.) Since that time, the space shuttle fleet has flown 115 missions.

I also remember using free time to test out those great new video games. Who can forget Frogger, Galaga, and Donkey Kong, all introduced in 1981. I wish I would have used more of that time studying! While we were enjoying these games, we also watched a fledgling cable network – introduced August 1 – that played music on TV: MTV.

On August 12, IBM rolled out the one technology item that has probably had the biggest effect on us techies: the IBM 5150 personal computer. This beige box, with a starting price of \$1,565, had a mere 16 kB of memory and used audio cassettes to load and save data. (A floppy disk drive was optional.) IBM's press release trumpeted the screen's "green phosphor characters for reading comfort" and "easily understood operation manuals" that made it "possible to begin using the computer within hours."

IBM's wasn't the first home computer, but Commodore's, Apple's, and Radio Shack's Tandy products were considered "toys." The IBM name added credibility that brought trust to the business environment.

eTForecasts estimates 25-year sales of MS-DOS and Windows PCs based on the original IBM PC architecture:

- *In the United States:* Unit shipments have totaled 580 million and represent U.S. \$998 billion, August 1981 to August 2006

- *Worldwide:* Unit shipments have totaled 1,540 million and represent U.S. \$3,100 billion, August 1981 to August 2006

The revenue figures include initial hardware sales only and exclude PC software and services. The software and services sales are probably several times these numbers!

Some of the other computer technology from 1981 that might trigger a memory or two include: the TFC 3450 by Fujitsu, the Commodore VIC-20, the Sinclair ZX81, the Osborne I (who can forget!), the TI-99/4A, the IBM System/23, the Epson HX-20, the Rockwell AIM 65/40 (I cut my teeth on assembly programming on this machine), and the Dynabyte 5100.

In an HP laboratory in Corvallis, Oregon, an Iowa farm-boy-turned-PhD (not me) was about to introduce the HP 12c Financial Calculator. After 25 years, this calculator is still sold under its original name and model.

In late 1981, after several committee meetings and after a number of other companies decided to adopt the combined standard, the NCR BYSE (Byte Serial) and SASI (Shugart Associates System Interface) was introduced under the new name "SCSI."

With all this going on, it's hard to imagine any other great technologies emerging from all the press releases, but it happened! On October 21 (for some reason the numbers 1 and 2 show up in a lot of these introduction dates – maybe this means something to you numerologists out there), there was a small innocuous press release issued from Brussels, Munich, and Hamburg that was to forever change the embedded computing segment of the technology world. The headline declared "Mostek, Motorola, Philips/Signetics, and Thomson CSF announce a common system bus for 16/32-bit computer systems." Of course, they were talking about VMEbus.

The announcing companies were claiming that this technology would be great for process control technology, data technology, intelligent terminals, and digital communication networks.

VMEbus is in some great company. It is a technology that has great staying power, has adapted to the changing needs of its users, and has embraced change as it matures. VMEbus has aged very well. I look forward to the changes that are ahead in the next 25 years.

VMEbus, happy anniversary!

For more information, contact Jerry Gipper at jgipper@opensystems-publishing.com.

8 / FALL 2006 MILITARY EMBEDDED SYSTEMS

# Leading the way in **Digital Receiver Technology**

When only the best is good enough.

Delivering the best solution means not making compromises. Not compromising performance – when you could have the industry-leading sustained performance of the ICS-8552B or ICS-8554. Not compromising reliability - when you could have the world-beating expertise of ICS in developing rugged solutions. Not compromising choice - when the ICS-8552B and ICS-8554 provide the best in ADC, DDC and FPGA technology for software defined radio, military communications, radar and signal intelligence applications. And not compromising your budget when you can choose the optimum solution for either development or deployment.

Or is second best good enough?

ICS-8552B

## **Brilliant inventor or patent troll?**

By Jim Turley

Software is a lot like prostitution. You get to sell it, then sell the same thing again to someone else. It's a service industry. There's no inventory, no cost of goods, and no manufacturing problems. It's labor-intensive. There's very little overhead, and the profit margin approaches 100 percent. The *product*, unfortunately, depreciates rapidly with age. And yet, like the world's oldest profession, hardly anyone in the software business – with a few notable exceptions – ever gets rich at it.

Despite all these similarities, most people *like* software companies (again, with one or two exceptions). We look favorably upon the software industry as a beneficial and valuable part of the high-tech community. Nobody seeks to ban software or make it illegal, or to rein in software development or progress. On the contrary, we're training new programmers here and in other countries at a fantastic clip. We want more, please.

Even though there's only a thin line separating these two business models, nobody seems to confuse prostitutes with programmers. We instinctively know the difference between hookers and coders, between women of ill repute and techies of questionable hygiene.

Patents and copyrights are a lot like software, too. There's no tangible product there, but we still know there's real value. We applaud inventors like Thomas Edison for his creative genius and his patented inventions, even though he never actually mass-produced anything. All the light bulbs, phonographs, and whatnot were built by other companies under license.

Edison would be less revered if he'd kept all his inventions to himself, hoarding the patents and preventing anyone from making commercial use of them. What good is an invention if no one gets to use it? The whole point of a patent is to promote commercial exploitation; you're *supposed* to share it. Otherwise it's called a trade secret (like the recipe to Diet Coke).

It's good to share, as we learned in grade school. In the high-tech world, it's also profitable. Companies with interesting inventions are encouraged to patent and therefore share them. Companies that can't – or don't wish to – manufacture products can still participate a little in the success of the products they invented.

Of course, there's always some risk with sharing. Someone might want to steal your property (intellectual or otherwise) and use it for free. In high-tech patent suits, as in some European soccer games, there's a tendency for one party to fall down and cry "patent troll," shedding alligator tears to gain sympathy and deflect attention away from their illegal behavior.

A real patent troll is a person or company that extorts money for a patent it has no intention of using. An example would be a law firm that buys up patents for no other reason than to milk them for income. That's a lot different from a high-tech company that's been granted its own patents for inventions it developed that were used in its own products and offered for license. Like programmers and prostitutes, there's a big difference between the two, but some observers still tar them both with the same brush.

Yes, Virginia, there really are patent trolls, but they're not lurking under every high-tech bridge throughout the hardware and software landscape. Just because a company enforces its patent rights doesn't make it a patent troll or a bad guy. Jeer at the law firms if you want, but spare a cheer for the high-tech hardware and software companies that have invented things, shared them with the world, and maybe made a living from their inventions.

Jim Turley is an independent analyst covering microprocessors, embedded systems, intellectual property licensing, and semiconductors. He writes, presents, and consults with high-technology firms throughout the world. He is also a member of the board at Patriot Scientific. Jim is the author of seven books and hundreds of articles. He was previously editor-in-chief of Embedded Systems Design magazine and editor of the journal Microprocessor Report. He is frequently quoted in The Wall Street Journal, The New York Times, San Jose Mercury News, and appears on TV, radio, and Internet broadcasts. He has a stunningly attractive wife, two overachieving children, and an apparently brain-damaged dog.

For more information, contact Jim at jim@jimturley.com.

10 / FALL 2006 MILITARY EMBEDDED SYSTEMS

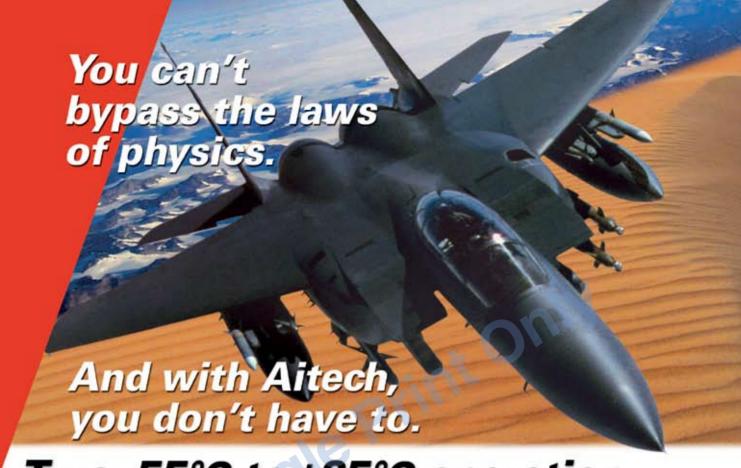

# True -55°C to +85°C operation... Standard!

Aitech continues to provide industry standard open systems architectures such as VMEbus and CompactPCI products, designed and tested to -55°C to +85°C as standard, because you can't bypass the rules of engagement either.

We can't change the physics... but we can ensure your COTS sub-systems are designed, built, and tested to perform reliably at the temperature extremes of your specification — without custom development, "work-arounds", or compromises.

We take the extra steps... including pre-screened parts qualification, HALT, and 100% HASS/ESS testing to ensure that every standard Aitech product meets all your temperature and rugged performance specifications...standard.

We've been there... Aitech subsystems have been proven in the world's most demanding mission-critical mil/aero applications — from complex ground, air and sea platforms to rad-tolerant solutions for the Space Shuttle, International Space Station and now earth orbiting satellites!

We've done that... Meeting full temperature-range specifications with standard products is just part of our 20+ year heritage and commitment to COTS advancements – from the first conduction-cooled Mil-Spec VME board in 1984, to today's highest functionality MIPS/Watt boards, multi-Gigabyte mass Flash mass memory cards, and high-speed mezzanines.

We have the proof...Visit our web site or call for more information and our catalog of proven solutions.

Aitech Defense Systems, Inc.

9301 Oakdale Avenue

Chatsworth, CA 91311

email: sales@rugged.com

Toll Free: 888-Aitech8 - (888) 248-3248

Fax: (818) 718-9787

www.rugged.com

RSC# 11 @www.mil-embedded.com/rsc

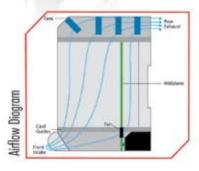

# Improved cooling technologies for both power-supply and motor-drive military applications

By Ralph Remsburg

Power dissipation problems are requiring increasingly complex design solutions. While designs that are more efficient make thermal management possible, current chips and systems still require sophisticated methods for dissipating heat. Several different fin geometries might be used to cool a three-chip, 1,080 W Insulated Gate Bipolar Transistor (IGBT) copper cold plate. The geometries are compared using maximum junction temperature and efficiency. One manufacturing method, Metal Injection Molding (MIM), appears to meet the thermal objectives and is examined more closely.

Insulated Gate Bipolar Transistors (IGBTs) generally are used as switching components in inverter circuits in both power-supply and motor-drive military applications. Although very efficient, these modules suffer from conduction and switching-power losses, which generate heat that must be conducted away from the power chips into the environment.

Previously, familiar air-cooled aluminum heat sinks were sufficient for this heat conduction. But as some military converter and inverter circuit applications reached multi-megawatt requirements, the more thermally effective approach of liquid cooling using copper cold plates has become more common. Cold plates have been improved with more capable designs that utilize lanced-offset fins to replace serpentine-tube cold plates. However, the space constraints of shrinking cold plates - and the strict demand to lower cost - have created a need for even more efficient heat-transfer surfaces within the cold plate.

Innovative designs utilizing impingement flow paths and microchannel surfaces

are starting to be used. A manufacturing process called *Model Injection Molding* (MIM) makes highly efficient nonlinear fin arrays. A *fin*, technically referred to as an extended surface, is a protrusion from a heated surface that provides more surface area for heat dissipation. A fin array or fin pattern usually takes the form of a repeating series of identical fins with identical spacing between fins. The exact shape and spacing between fins can have a dramatic effect on the amount of heat that can be dissipated from a surface, and hence, the junction temperature of a device mounted to that surface.

#### Fin comparison

While there have been many studies of single cooling fin geometry parameters, the conclusions often conflict or can be applied only over a narrow range of variables. A review of the literature reveals that most studies of single-fin geometry neglect the importance of pressure drop, which for most real-world liquid-cooling systems is directly related to thermal performance by the pump flow curve. Even when the literature agrees on the relative performance of a single fin, these findings may become distorted when multiple, identical fin flow fields interact within a fin array.

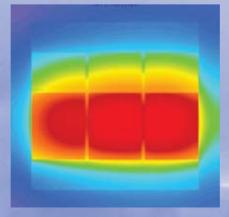

Figure 1

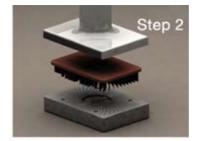

Figure 1 shows a 50 mm x 50 mm IGBT module containing three IGBT chips dissipating 300 W each and three diodes dissipating 60 W each. The total power dissipation is 1,080 W. Simulations were run using seven different extended surfaces to find the best-performing surface in terms of heat transfer coefficient, volumetric efficiency, and use of minimum pumping power.

To simulate the cooling capability of the various fin patterns, Flomerics Inc. Flotherm v6.1 software was used. Flotherm is a Computational Fluid Dynamics (CFD) analysis tool widely used in the electronics-cooling industry. For each simulation, the ambient air temperature is 80 °C. Radiation effects are not included in the analysis. The steady-state temperature distribution, fluid velocity, and pressure drop were recorded as the volumetric flow rate was increased from 1 liter/minute to 20 liters/ minute. The details of the seven cooling patterns are shown in Table 1. The x-axis is parallel to the fluid flow.

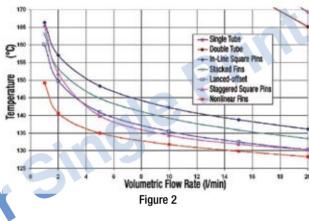

Figure 2 shows a thermal comparison of the various fin geometries. The curves represent the maximum semiconductor junction temperature when using a 30 percent EGW mixture having an inlet temperature of 80 °C to cool the 1,080 W IGBT module described.

Note that using the double-pass tube has roughly the same temperature result at 20 liters/minute as the staggered square pin pattern has at 1 liter/minute. The nonlinear array shows a lower junction temperature at all simulated flow rates. The single and double pass tubes would probably have unacceptable results in a cooling system unless the system could supply a large volume of coolant at low

| Pattern          | # Fins<br>in x | # Fins<br>in y | Diameter or thickness (mm) | Fin area<br>(cm²) |  |  |

|------------------|----------------|----------------|----------------------------|-------------------|--|--|

| Single tube      | -              | -              | 10.0                       | 15.7              |  |  |

| Double tube      | -              | -              | 10.0                       | 31.4              |  |  |

| Stacked fins     | 49             | -              | 0.20                       | 245               |  |  |

| Square in-line   | 31             | 31             | 0.785                      | 151               |  |  |

| Square staggered | 31             | 31             | 0.785                      | 151               |  |  |

| Lanced-offset    | 49             | 8              | 0.20 x 3.5                 | 137               |  |  |

| Nonlinear        | -              | -              | 0.5                        | 135               |  |  |

Table 1

pressure. In this 1,080 W application, the nonlinear array has an 11.2 °C lower junction temperature at 1 liter/minute than the next best performing geometry, which is the lanced-offset fin pattern. At 20 liters/minute, the nonlinear array maintains a 2.0 °C lower junction

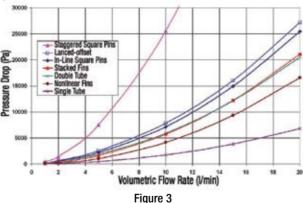

Figure 3 shows a comparison of pressure drop results for the simulation series.

temperature.

The staggered square pins, although producing a good result in terms of temperature rise (second to the nonlinear array), have a high-pressure requirement. At 20 liters/minute, the staggered square pins have nearly 4.3x the fluid resistance as the nonlinear array.

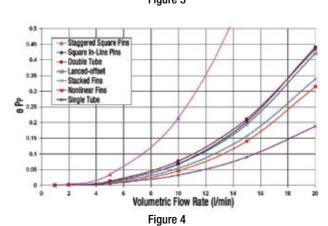

Figure 4 shows the relative efficiency of the fin patterns when compared using a metric of  $\theta P_p$  which is the product of °C/W and watts of pumping power. The lower the value, the more efficient the fin pattern. As noted previously, the staggered pin pattern has

RSC# 13 @www.mil-embedded.com/rsc

Blend copper powder and polymer binder

Injection molding into steel tooling

Polymer binder burns off, part shrinks 20%, and only copper remains

Take "green" part and send through sintering over

Figure 5

good thermal performance but a very high-pressure drop. Therefore, efficiency is low.

According to data presented in Figure 4, the best surface in terms of efficiency is the single-pass tube. Although the efficiency is high, the lack of surface area and the resulting high junction temperature may preclude the use of this type of cold plate for cooling high-power modules. The nonlinear array performs better than all the other tested configurations in terms of junction temperature and has a relatively low pressure drop and, therefore, high efficiency. Because of the high efficiency, the nonlinear array may have advantages when it's used in low- and high-power applications.

#### Nonlinear fin arrays

In a nonlinear fin array, extensive CFD analysis ensures that each fin is optimized for maximum performance while simultaneously accounting for the performance flow fields of the fins adjacent to it in the array.

There are only a few processes that can economically produce a nonlinear

fin array. MIM is one of the most flexible. Using combined patented and proprietary technology to address thermal management challenges in the computing and other industries, MIM injection-molding technology was developed by Amulaire Thermal Technology.

Figure 5 shows the sequence used to make a MIM part. First, a mixture of powdered metal and polymer binders is molded into the desired shape. The part is removed from the mold and sintered at high temperatures to remove the polymer binders so that no extraneous material remains in the final product. Sintering also bonds the metal particles. During sintering, while the polymer binder debinds and vaporizes, the parts shrink in a uniform and controlled manner. Usually a net shape is achieved with no need of further processing.

Cold places made using this MIM process can have more pin fins to increase the surface area of the cold plate, and they can have highly complex nonlinear fin patterns. One recently developed cold plate, for example, contained 5,000 pin fins in a 5 x 5 inch area. Amulaire has also designed compact and unique fin pattern solutions for dissipating nearly 6,000 W, utilizing the MIM process, as shown in Figure 6.

Figure 7 shows a top view of the flow field of the optimized nonlinear fin array utilizing an impingement flow pattern used in this simulation. Each fin is individually designed to take advantage of the existing direction of fluid flow,

Figure 6

## DESERT DESIGN TECHNIQUES: PHYSICS FIRST—Hardware

Figure 7

minimizing pressure drop while offering an optimized heat transfer surface area. The inlet coolant flow impinges at the center of the fin pattern. Round pins at the center transfer heat directly from the hottest part of the IGBT module into the fluid area of the cold plate having the highest fluid velocity and highest heat-transfer coefficient.

As the fluid moves outward from the point of impingement and the velocity decreases, the round fins change shape to ellipses to take advantage of the direction of fluid flow and offer more surface area. Although the surface area of each fin is greater in this area, the pressure drop does not increase greatly because the fluid is moving slower.

As the fluid approaches the exit ports, velocity starts to increase. Again the fins change shape, but from elliptical to round. At the same flow rate, this nonlinear design results in a significant reduction in maximum temperature from the lanced offset fin pattern of Table 1, which would be the typical choice used to cool the module. Because the objective of thermal management specialists is to eliminate problems in heat transfer at the component and system levels, these results show that a properly designed heat sink using a nonlinear fin array can make an important contribution to that goal.

# Increased reliability and performance

A recently developed MIM technology enables the development of cold plates for IGBTs with superior heat-dissipation capabilities. This new approach to IGBT cold plates has implications for both power-supply and motor-drive military applications.

As component designers work to increase the power capabilities of IGBT modules, it becomes more difficult for system designers to stay below the maximum temperatures specified in the manufacturer's data sheets. As temperatures are reduced, reliability and available performance increase. For example, some data shows that reducing the junction temperature 50 °C can lead to a 33x life extension (6,000 cycles at 100 °C, 200,000 cycles at 50 °C). Increasing the level of fin sophistication from standard machined fins to nonlinear fins can put these levels of performance and reliability within the reach of system designers at a competitive price point.

Ralph Remsburg is chief engineer at Amulaire Thermal Technology. In addition to having acquired more than 20 years of experience as a thermal

specialist, he has written two books on the thermal design of electronic equipment and holds 15 patents.

To learn more, contact Ralph at:

#### **Amulaire Thermal Technology**

11555 Sorrento Valley Road San Diego, CA 92121 Tel: 858-309-4718

Fax: 858-481-6817

E-mail: ralphr@amulaire.com Website: www.amulaire.com

RSC# 15 @www.mil-embedded.com/rsc

# Adaptive meshing helps Army develop Future Combat Systems

**CFD software models muzzle recoil**

By Jerry Fireman

software that automatically

the blast wave.

soldiers.

increases mesh density in the area of

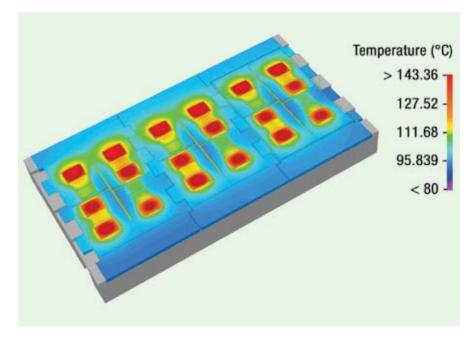

Muzzle brakes are needed to shield the Army's new generation of much lighter combat vehicles from the recoil of guns that are just as powerful as those used on previous generation vehicles. Computer simulation is being used to ensure that the gun's propellant flow does not injure soldiers or damage the vehicle. The key to successfully simulating blast overpressure is Computational Fluid Dynamics (CFD)

One of the centerpieces of the Army's

Future Combat Systems (FCS) program is the

development of new combat vehicles that are only about

one-fourth to one-half the weight of the Army's current vehicles,

yet capable of mounting guns that are as powerful as the older

vehicles' guns. To meet this goal, the new lighter vehicles require

muzzle brakes that redirect part of the gun's propellant flow

backwards to reduce the gun's recoil. But this redirection must be

accomplished while keeping the blast overpressure on the vehicle

The conventional approach to mesh adaption ... is not ideal for this problem because it puts more elements on the stronger waves ...

itself low enough to prevent vehicle damage and injury to nearby

Testing proposed muzzle brake designs is very expensive and time consuming. The engineers at the Army's Benét Laboratories in Watervliet, New York are therefore using a new generation of CFD software to model the gun's recoil forces and blast pressures for different muzzle brake designs to provide optimized solutions of low recoil force with acceptable blast overpressure. The key to their success in modeling blast overpressure has been

the development and use of CFD software that automatically increases the density of the computational mesh in the area of the blast wave to provide the required accuracy while keeping the mesh unchanged in other areas where the increased detail is not needed. With future code improvements, this will help them get the accuracy they need, where they need it, without the expense of excessive computation times.

Image courtesy of U.S. Army

#### Replacing the current fleet of combat vehicles

The FCS, the Army's flagship transformation program, is a networked array of systems that uses advanced communications and technologies to integrate the soldier with manned and unmanned platforms and sensors. The Army transformation requirements include the ability to put a combat-capable brigade anywhere in the world within 96 hours, a full division in 120 hours, and five divisions on the ground within 30 days. To meet this goal, FCS will, over time, replace the current fleet of heavy vehicles – the M1 Abrams tanks and M2/M3 Bradley Fighting Vehicles – with a new family of lighter and smaller manned and unmanned ground vehicles and aerial vehicles.

The maximum essential combat configuration weight for the FCS family of systems will be 19 tons. These lighter, smaller vehicles are designed to fit into a C-130-like plane. The C-130 is capable of landing on smaller and less developed landing strips, making

it possible to deliver more vehicles closer to where they are needed. The first FCS unit will be fielded in 2008, with 32 brigades equipped by 2014.

#### Designing a muzzle brake

The U.S. Army Armament Research, Development and Engineering Center's (ARDEC's) Weapon Systems & Technology (WST)/Benét Laboratories are colocated at the Watervliet Arsenal in upstate New York. Benét has been assigned the responsibility for designing the muzzle brake of the Mounted Combat

System (MCS) tank cannon and the Non-Line of Sight Cannon (NLOS-C) artillery cannon, which are designed to replace the Abrams tanks and Paladin artillery vehicles as the Army's primary fighting and artillery vehicles.

The 19-ton MCS isn't heavy enough to absorb the full recoil force of its 120 mm gun, which fires as powerful ammunition as the 70- to 80-ton Abrams tank. So the MCS will use a muzzle brake to reduce the recoil, a device that is analogous to the thrust reversers that are used to slow down jet airliners after landing. The muzzle brake is a series of holes in the gun tube near the muzzle, through which the gas vents.

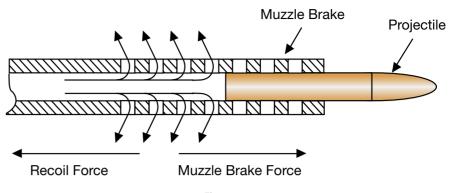

Figure 1 depicts a typical perforated muzzle brake operation. As a projectile passes the muzzle brake holes and flow begins to act on the gun tube, a force is generated opposing the recoil force. The venting process pulls the tube forward to counteract the recoil.

The design challenge is to reduce the recoil without putting excessive blast pressure on the vehicle. The challenge is complicated by the fact that a portion of the blast that hits the ground may be redirected back to the vehicle. A blast deflector may be used in an effort to funnel the blast waves coming out

of the muzzle brake to the side rather than back towards the vehicle. It is important to be able to evaluate the performance of proposed muzzle brake and blast deflector designs with CFD, because it is expensive to build and test prototypes. Simulation also has the advantage of being able to determine peak pressures generated by exhaust gases at all points on the vehicle so that the vehicle can be designed to withstand them.

## Challenges of simulating a blast wave

Despite the advantages that it offers, simulation presents its own special challenges. The motion of the blast

Figure 1

wave must be modeled through a large volume of space. Mesh sizes of 0.5 mm or smaller are required at the edge of the blast wave in order to accurately capture the short-lived transients. When the mesh is coarser than this value, it artificially spreads out the blast wave and reduces the accuracy of peak pressure predictions. Having the mesh this fine throughout the entire solution domain, however, would increase the model size to the point where it would have theoretically taken centuries to solve, even on the fastest available computing hardware. Steady-state problems involving steep gradients, such as those occurring at shock fronts, are addressed by using a fine grid in one small region of the computational domain (that containing the most prominent gradients). In this case, however, the steep gradients associated with the blast wave rapidly sweep through the entire domain, so a novel approach is required to simulate the moving blast wave properly.

To overcome this problem, Benét Laboratories is taking advantage of the easy-to-use dynamic adaption capabilities of FLUENT CFD software from Fluent Incorporated, Lebanon, New Hampshire. CFD works by discretizing the flow domain into small cells, the sum of which is called a mesh, so that an algorithm can be applied to simultaneously solve the equations of motion for each cell. Dynamic adaption continually changes the density of the mesh throughout the domain so that as the

MILITARY EMBEDDED SYSTEMS FALL 2006 / 17

blast wave propagates, the mesh in the area surrounding it is made finer. Regions that were refined earlier in the calculation are coarsened to a reduced mesh density, if the conditions there no longer require the increased detail. FLUENT allows the user to select the criteria upon which the mesh is refined or coarsened. Adaption based on the absolute pressure level has proven most effective for Benét to date, providing sufficient accuracy

throughout the model without excessive computation time.

#### Validation case

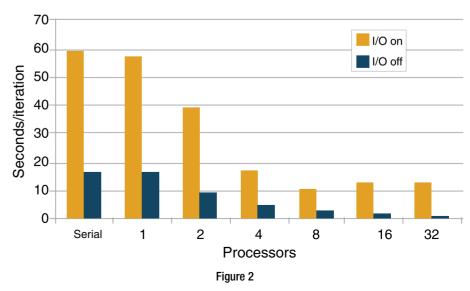

In order to validate the accuracy of the simulation, Benét engineers modeled a test rig at the Aberdeen Proving Ground consisting of the gun, mounted on a stand, that will go into the MCS. The simulation was performed on a Linux Networx 32-processor cluster with a Myrinet backbone and METIS load balancing. Engineers configured the zonal adaption capabilities of FLUENT to adapt the mesh every 15 time steps and to increase the number of elements in areas of high pressure by a maximum factor of 32. This simulation began at 1.7 million cells and increased to a peak of 34 million cells through adaption. Figure 2 shows how Linux Networx 32-processor cluster performance increases as more processors are utilized.

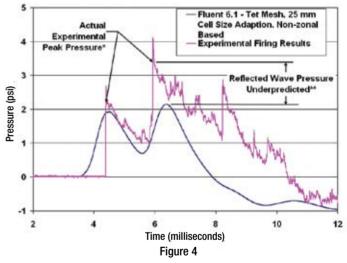

The test rig used to validate the simulation is shown in Figure 3. The validation case comparing FLUENT 6.1 results to experimental gun firing for the test is shown in Figure 4. Comparing the simulation predictions to physical testing has shown that CFD accurately predicts the primary or first blast wave peak pressures, but the pressure history below indicates that the CFD results for the peak pressures associated with the waves that are reflected from the ground are lower than the measured values. Furthermore, the

shape of the pressure waves predicted by CFD are much gentler than their measured counterparts. Note the type of pressure transducer used to acquire experimental data overshoots. It is known that the actual pressure is closer to what was predicted in the simulation.

In addition, reflected wave pressures are underpredicted by FLUENT due to lack of mesh resolution. A more finely resolved mesh would yield higher peak pressures and steeper waves, but there is always a trade-off between accuracy and computational expense. For example, had this validation been performed with a significantly finer adapted mesh

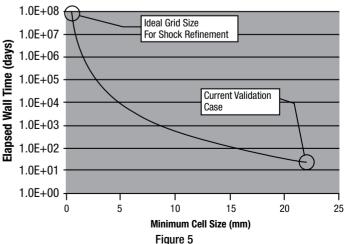

resolution, such as with a minimum cell dimension of 0.5 mm instead of 25 mm, the calculation would have taken many years.

The chart in Figure 5 shows how an increase in mesh resolution to the ideal size would increase solution time to centuries. This problem is addressed with mesh adaption. The conventional approach to mesh adaption, which adapts the mesh based on a fixed criterion throughout the entire flow domain, is not ideal for this problem because it puts more elements on the stronger waves that move forward out of the muzzle and fewer elements on the weaker but more important waves coming out of the muzzle brake and moving back toward the vehicle. Most recently, Benét has been using a new version of FLUENT that allows users to set different criteria for adaption in different areas of the computational domain. This so-called *zonal-based adaption* has demonstrated advantages by making it possible to focus computing resources on the most important sections of the blast wave – those moving toward the vehicle.

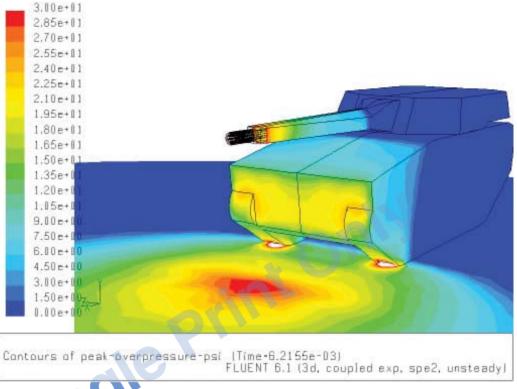

But even without zone-based criteria, the CFD analysis via dynamic adaption was found to yield reliable results. With the model having been validated, Benét engineers are using it to evaluate alternative design configurations. For example, Figure 6 shows CFD results with the muzzle brake installed. The results of each simulation show peak pressure levels on the vehicle and can easily be animated to show the movement of the blast wave over time. This capability, which makes proposed changes easier to evaluate, will dramatically reduce the amount of time required to design the next-generation gun for the Army's number one fighting vehicle.

Figure 6

Jerry Fireman is president and founder of Structured Information, a marketing communications firm representing Fluent Inc. and Benét Laboratories. Jerry can be reached at jerry\_fireman@strucinfo.com.

This article was written with input from Dan Cler, Senior Mechanical Engineer, Benét Laboratories, Watervliet, New York and Christoph Hiemcke, Senior Business Services Engineer, Fluent Inc., Lebanon, New Hampshire.

For more information, contact:

#### Fluent Inc.

10 Cavendish Court Centerra Resource Park Lebanon, NH 03766 Tel: 603-643-2600

Website: www.fluent.com

#### **Benét Laboratories**

Technology Transfer Office 10 Buffington Street Watervliet, NY 12189

Tel: 518-266-4325

Website: www.benet.wva.army.mil

# Using resource partitioning to build secure, survivable military systems

By Paul N. Leroux and Kerry Johnson

Network-centric warfare relies heavily on interconnected platforms, weapons, communications, and sensor systems. Of course, each of these "system of systems" contains its own intelligence, which also makes each vulnerable to software glitches, malicious attacks, or simply buggy code. One way to assure that a problem in one system doesn't affect the entire Global Information Grid (GIG) is to use partitioned operating systems. In addition, partitioned environments also offer protection from priority inversions, resource starvation, and other inadvertent but not uncommon software behavior.

By providing access to accurate, timely information from virtually any location, the GIG promises to help war fighters identify and eliminate enemy threats with unprecedented efficiency. Nonetheless, the GIG mandate of networking all military systems will inevitably introduce its own threats, including viruses, Denial-of-Service (DoS) attacks, and other forms of cyber sabotage. To contain such attacks and ensure constant availability of mission-critical services, partitioning provides every software subsystem with a guaranteed share of computing resources.

#### Limited resources

Safeguarding the reliability and security of net-centric warfare systems represents a significant challenge – a challenge made

all the more difficult by the complexity of modern software. This complexity can undermine reliability for the simple reason that the more code a system contains, the greater the probability that coding errors or unanticipated software interactions will make their way into the field. It can also compromise security because hackers typically exploit such errors when they wish to damage or infiltrate a system. Unfortunately, no amount of testing can fully eliminate these problems, as no test suite could possibly anticipate every scenario that a complex software system may encounter.

The process of developing software for military systems presents a further complication. An integrator building a ground-vehicle system, for example, may need to integrate application programs from one vendor, protocol stacks from another,

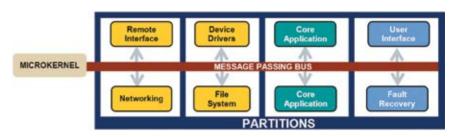

an RTOS from yet another, and an embedded database from still another. The integrator must then combine those components with multiple software subsystems developed in-house, each written by a separate development group. Figure 1 shows some of the many software components that such a system may comprise.

Given the parallel development paths, performance problems invariably arise at the integration phase, when, for the first time, the various subsystems begin vying with one other for CPU time and other system resources. Subsystems that worked well in isolation now respond slowly, if at all. Unfortunately, many of these issues emerge only during integration and verification testing, when the cost of software redesign and recoding is at its highest.

To maintain secure operation and integrate multiple software subsystems successfully, the integrator must implement an architecture that prevents any component or subsystem from corrupting or monopolizing the computing resources (for example, memory and CPU time) that other subsystems require. Integrators could, in theory, achieve this goal by using hardware partitioning, an approach that uses a separate board or node to run each software subsystem or group of subsystems. Such an approach can both contain faults and reduce competition for shared resources. In military systems, however, the trend is toward integrating more

Figure 1

functionality into a single slot. Such an approach not only cuts costs ("saving slots saves money"), but also minimizes weight and power consumption.

#### Secure compartments

To address these security and integration issues, some designs place virtual compartments, or *partitions*, around groups of software processes

and allocate a predetermined set of resources, including CPU time, to each partition (Figure 2). The system can thus prevent processes in any partition from inadvertently or maliciously monopolizing resources needed by processes in other partitions. In the Defense and Aerospace (D&A) industry, many partitioned systems comply with the ARINC 653 specification, which provides a well-known though somewhat rigid and inefficient approach to resource partitioning.

Among other things, partitions can provide memory protection where the OS uses the Memory Management Unit (MMU) to control all memory access. A microkernel operating system, for instance, can partition applications, device drivers, protocol stacks, and file systems into separate, memory-protected processes. If any process, such as a device driver, attempts to access memory outside of its process container, the MMU will notify the OS, which can then terminate and restart the process.

This approach offers an immediate and measurable improvement to system reliability:

- Prevents coding errors in any process from corrupting other processes or the OS kernel

- Allows the developer to quickly identify, diagnose, and correct violations that could otherwise take weeks to isolate

- Reduces fault-recovery times dramatically: Rather than having to reboot when a memory violation occurs, the system can simply restart the offending process

#### **Avoiding task starvation**

Nonetheless, building a reliable system involves more than partitioning functionality into separate memory domains. For many systems, ensuring resource availability is also critical. If a key subsystem is deprived of CPU cycles, for example, the services provided by that subsystem will become unavailable to users. In a DoS attack, for instance, an external system could bombard a device with requests that need to be handled by a high-priority process. That process will then overload the CPU and starve other processes of CPU cycles, making the system unavailable to users.

Also, in many cases, adding software functionality to a system can push it "over the brink" and starve existing applications of CPU time. Historically, the only solution was to either retrofit hardware or redesign software.

Figure 2

#### **Fixed partition schedulers**

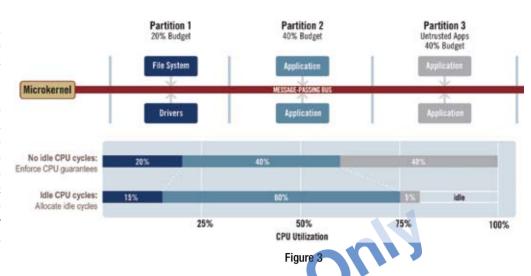

To address these problems, some operating systems offer a fixed-cycle partition scheduler, typically based on ARINC 653, that allows the system designer to group processes into partitions and to allocate a percentage of CPU time to each partition. With this approach, no process in any given partition can consume more than the partition's statically defined percentage of CPU time (for instance, 20 percent of the CPU).

Fixed-cycle schedulers have their drawbacks, however. Since the scheduling algorithm is fixed, partitions that aren't busy consume their allocated CPU cycles in an idle state. Meanwhile, other partitions can't access those unused cycles, even when they are busy and could benefit from the extra processing time. This approach squanders valuable (and available) CPU cycles and prevents the system from handling burst demands. Because of this "use it or lose it" approach, fixed partition schedulers can achieve only 70 percent CPU utilization.

# Partitioning on multicore processors

Like systems in every other industry, mission computers and subsystems for radar, flight control, and sensor fusion are growing in complexity, with a voracious appetite for computational power. Multicore processors offer the ideal performance upgrade for such systems by delivering significantly greater performance per watt, ounce, and square inch than conventional uniprocessor chips. In fact, system designers will have little choice but to embrace multicore technology, since it forms the basis of most new processor designs.

Thus, an operating system must be able to support resource partitioning on multicore hardware. Unfortunately, most legacy RTOSs, including those with partitioning schedulers, can control only one CPU or processor core at a time. Developers must, as a result, run a separate copy of the RTOS on each core of the multicore chip. Because neither copy owns the entire system, the application designer, not the OS, must handle the complex task of managing the chip's shared hardware resources, including physical memory, peripheral usage, and interrupt handling. To avoid this complexity, systems designers should choose an RTOS that can control multiple cores simultaneously, manage shared resources, and provide dynamic load balancing across cores — while still enforcing resource guarantees.

### Software—operating systems

This cap on CPU utilization presents several undesirable choices to the system designer: Use a faster, hotter, more-expensive processor; limit the amount of software functionality that the system can handle; or simply tolerate slower performance. cap also presents a "double whammy" to designs that must keep a significant percentage of CPU cycles in reserve for future applications or system enhancements.

Also, to request OS services or to communicate with other processes, applications must use the APEX interface as defined in the ARINC standard. This restriction prohibits legacy applications from leveraging the benefits of secure partitioning.

#### Adaptive partitioning schedulers

Another approach, called *adaptive partitioning*, addresses these drawbacks by providing a more dynamic scheduling algorithm. Similar to fixed-cycle partitioning, it allows the system designer

DataMetrics' As pioneers and innovators of ruggedized Information Technology equipment for the past 44 years, our designs have been proven in extreme environments and harsh applications time and time again. Whether our products are deployed in the sands of the Middle East, or monitoring grade levels in a North Dakota coal mine in the dead of winter, our products perform and last DataMetrics designs and manufactures conduction and convection-cooled ATR, rackmount and bulkhead mounted chassis that support VME, VME64x, VITA41 (VXS), CompactPCI and customer-specific bus architectures, and also integrates complete rugged computer systems. For a sampling of our chassis/enclosure products, go to the Product sec tion of our website Model 8000 VME-18 1717 Diplor Orlando, FL 32809 1-877-5RUGGED www.datametrics.com

RSC# 22 @www.mil-embedded.com/rsc

to reserve CPU cycles and memory for a process or group of processes. Designers can thus guarantee the load on one software subsystem won't affect the availability of other subsystems.

Unlike fixed approaches, however, adaptive partitioning recognizes that CPU utilization is sporadic and that one or more partitions can often have idle time available. Consequently, an adaptive partitioning scheduler will dynamically reallocate those idle CPU cycles to partitions that can benefit from the extra processing time. This approach, which was pioneered by QNX Software Systems, offers the best of both worlds: It can enforce CPU guarantees when the system runs out of excess cycles (for guaranteed availability of applications and services) and can dispense free CPU cycles when they become available (for maximum CPU utilization and performance). In Figure 3, for example, Partition 2 consumes no more than 40 percent of CPU cycles when the system is running at capacity. But it can consume more than 40 percent whenever other partitions require less than their allocated CPU budget.

Adaptive partitioning offers several other advantages, including the ability to:

- Use real-time, priority-based scheduling when the system is lightly loaded, allowing systems to use the same scheduling behavior that they do today

- Overlay the partitioning scheduler onto existing systems without code changes, enabling users to launch existing POSIX-based applications in a partition

- Achieve 100 percent CPU utilization in a controlled fashion, allowing integrators to realize the benefits of time partitioning without the need for faster, more expensive processors

- Guarantee that fault-detection and recovery operations have the CPU cycles they need to repair software faults, thereby improving Mean Time To Repair (MTTR)

- Allow operators to remotely monitor or troubleshoot the system without interrupting the availability of critical applications

- Stop malware and DoS attacks from stealing all available CPU time

While adaptive partitioning offers greater flexibility, fixed-cycle scheduling may be desirable in some situations. To address this requirement, an implementation of adaptive partitioning should allow the system designer to configure a system with fixed partition budgets and no CPU time "borrowing." This approach frees system designers to choose the most appropriate scheduling behavior for their application requirements.

**Conflicting demands**

Embedded software is becoming so complex that, without some form of partitioning, system designers and software engineers will be hard-pressed to satisfy the conflicting demands for reliability, performance, security, time to market, and new features.

With resource partitioning, vendors can readily integrate subsystems from multiple software teams, subcontractors, and third party developers; allow new and upgraded components to run without compromising existing system behavior; and contain the effects of DoS attacks and other network-based exploits. If the partitioning solution also provides a flexible, efficient scheduler that allows 100 percent CPU utilization, then vendors can realize these benefits without having to incur the cost of faster, more expensive hardware.

Kerry Johnson is a senior product manager at QNX Software Systems, where he is responsible for product road maps and introducing new technology to the embedded

market. He has 20 years' experience as a software design manager and project manager in companies such as Nortel, CrossKeys, and Research in Motion. He holds a Bachelor's of Applied Science in Electronic Information Systems Engineering from the University of Regina, Saskatchewan.

Paul Leroux is a technology analyst at QNX Software Systems whose interests include high availability design, multiprocessing systems, and OS kernel architecture.

For more information, contact Paul or Kerry at:

#### **QNX Software Systems**

175 Terence Matthews Crescent Ottawa, Ontario Canada, K2M 1W8

Tel: 613-591-0931 E-mail: info@qnx.com Website: www.qnx.com

RSC# 23 @www.mil-embedded.com/rsc

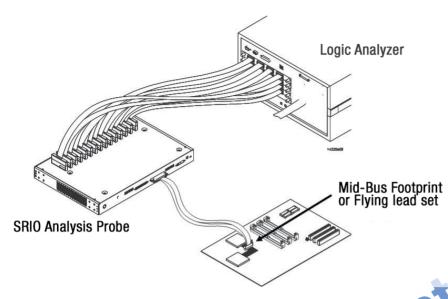

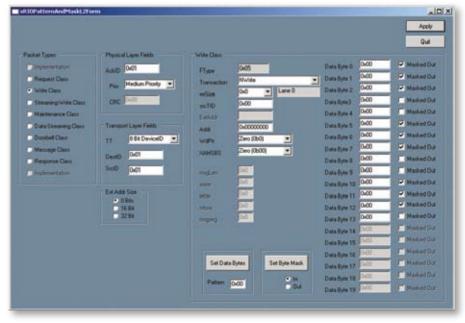

# Using your existing test and measurement platform to perform Serial RapidIO protocol analysis

By Barbara Aichinger

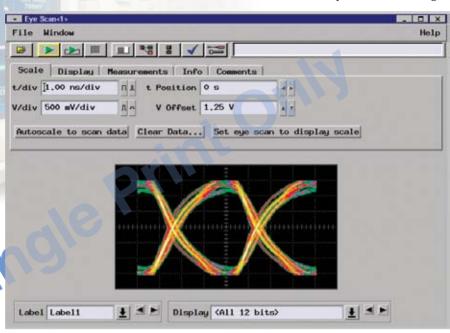

The Serial RapidIO (SRIO) standard is now meeting the need for increased bandwidth, lower latency, and faster interconnect speeds. But with increased performance comes new challenges in the validation and debug phases of product development. As design engineers migrate their skill sets from standard to standard, they also must migrate their lab debug skills and equipment to accommodate the newer, faster technologies. Do engineers need to go out and invest and learn a new set of tools? The surprising answer is "no."

Design validation of parallel buses is challenging but fairly straightforward. Parallel buses by nature are made up of an address bus, a data bus (sometimes multiplexed), control signals, and a clock. More sophisticated high-speed parallel buses may even contain several clocks, thus creating multiple time domains. The tools that engineers use to validate these buses are available and are a fairly close match, architecturally, to the task of attaching and decoding parallel buses. These tools are generally scopes and logic analyzers.

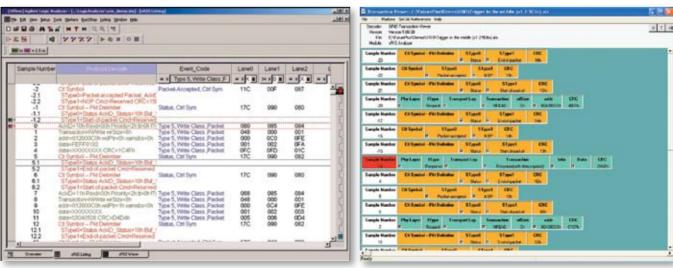

Figure 1

even in the absence of these specialized add-ons, engineers could observe parallel buses with just high-speed sampling. Armed with a timing diagram and the general output of the logic analyzer or scope, engineers could still get a rough idea of what was going on.

These serial interconnects such as Serial RapidIO are replacing parallel buses in today's systems; however, the function that these interconnects provides remains largely the same: They move data quickly and efficiently from one functional area to another. For design validation and debug, engineers still have the same issues including:

- Checking for general system integrity

- Looking for protocol errors to ensure specification compliance

- Finding events that lead up to a system hang up or lockup

- Measuring performance through devices

In many cases, specialized hardware and software for parallel bus analysis are available that attach to and run on a scope

The digital oscilloscope with its

low channel count and high-speed

sampling can still be used for serial

interconnect debug ...

With the advent of serial interconnects changing the overall computer architecture landscape, what will engineers do with their general purpose, parallel-busoriented test equipment?

But serial interconnects are different. Since the data is encoded and involves clock recovery, simple high-speed data sampling reveals only eye diagrams (see Figure 1).

24 / FALL 2006 MILITARY EMBEDDED SYSTEMS

or logic analyzer to help with protocol

decode and timing analysis. However,

# Annapolis Micro Systems The FPGA Systems Performance Leader!

FOPEN Radar Systems Software Defined Radio FLIR SIGINT ELINT Digital Receivers Recording Systems

High Performance

Signal Processing in

Scalable FPGA Computing

Above and Beyond -----

**FPGA Acceleration**

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland 21401 wfinfo@annapmicro.com (410) 841-2514 www.annapmicro.com

RSC# 25 @www.mil-embedded.com/rsc

©2006 OpenSystems Publishing. Not for distribution.

The digital oscilloscope with its low channel count and high-speed sampling can still be used for serial interconnect debug in that it can show compliance to the specification eye diagrams. By its very nature, the oscilloscope can make the transition from parallel bus debug tool to serial interconnect debug tool, but what about the logic analyzer? The logic analyzer sampling time is not fast enough, and for protocol state analysis, there is

The general purpose logic analyzer, when customized with analysis probes, lets users become familiar with one tool that is easily reconfigured for many different protocols and standards.

no separate signal that can be used as the clock. For serial interconnects protocol analysis, engineers now have to choose between a new dedicated serialinterconnect-oriented tool or a new innovative add-on to their existing logic analyzer.

# General purpose logic analyzer versus dedicated protocol analyzer

With the new Gbps serial interconnect standards, engineers must make some choices and accept some trade-offs when selecting validation and debug tools. One such choice is to select a *dedicated protocol analyzer*, or a general purpose *logic analyzer coupled with a serial interconnect analysis probe*.

A typical computer system employs multiple, different data bus and interconnect technologies, and each typically will require some debug and verification efforts. If one chooses dedicated protocol-analysis tools, then analyzing each bus or interconnect will require a different tool, each requiring a unique user interface to learn. Furthermore, acquiring a dedicated protocol analyzer for every interconnect implementation can add up to hundreds of thousands of dollars. When a particular technology inevitably is replaced by a newer one, the dedicated analyzer will be useless.

On the other hand, most digital designers already have made the financial and learning-curve investments in a general purpose logic analyzer. Using these with a single-instrument-based family of analysis probes, designers work with the familiar user interface for every protocol analyzer used.

RSC# 26 @www.mil-embedded.com/rsc

Figure 2

# Logic analyzer offers the greatest measurement flexibility and versatility

To meet the challenges of design validation and test complexity that result from higher speeds and denser designs, Serial RapidIQ designers need to look no further than their favorite logic analyzer vendor for a solution to these problems. Engineers have relied for decades on logic analyzers as an integral part of their validation and debug strategy. Analysis probes are essential to interface the logic analyzer with new, multigigabit (Gbps) architectures. Such probes sit between the target system and the logic analyzer, where they translate the high-speed serial interfaces into signals that can be processed by the logic analyzer (Figure 2).

On a single display, a single-instrument method offers the broadest spectrum of measurement capabilities, including crossdomain (simultaneous digital and analog) and cross-bus (simultaneous analysis of multiple protocols). Most analysis probes have software that facilitates intermodule collaboration, performs protocol decode, and simplifies triggering, store qualification, and performance monitoring of the device under test.

So the general purpose logic analyzer, when customized with analysis probes, lets users become familiar with one tool that is easily reconfigured for many different protocols and standards. Furthermore, the general purpose logic analyzer purchase can be more cost-

effective across more designs due to this customization ease. The new GUI that now accompanies most analysis probes and logic analyzers makes combining tools seamless and easy to use.

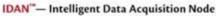

Specialized serial analysis probes include software that runs on the logic analyzer to give the user a complete decode of the packet protocol traffic. There is no need to look at cryptic hex or binary characters. Analysis of SRIO can be done from a highlevel graphical view or from a detailed text view (see Figures 3A and 3B, FuturePlus Systems FS4410 software).

# o lineed to buy a new logic analyzer?

Existing logic analysis equipment can be used, at a substantial savings, to analyze modern interconnects including, for example, PCI-X, Serial RapidIO, PCI Express, and DDR.

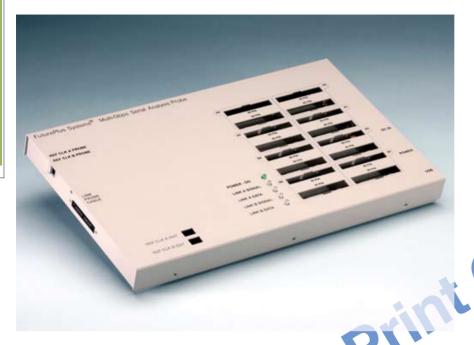

For an up-to-date example, the FuturePlus FS4410 analysis probe can provide up to 3.125 Gbps Serial RapidIO analysis (Figure 4). Users who also are working with PCI Express applications can use the same probe and incorporate the SRIO performance with 2.5 Gbps PCI Express analysis for a substantially lower cost than would be incurred by acquiring a separate probe for each purpose. Each of these high-speed serial standards can be debugged using just two of the previous generation Agilent 16753 series of logic analysis cards, which will work in both

Figures 3A and 3B

Pentium\* M cpuModules\*\*

8000 MIPS dspModules™

dspModules™

• Coprocessors

• Accelerators

Specialty I/O

utilityModules" -40 to +85°C

· Pulse width modulator Incremental encoder Opto-isolated MOSFET Frame Grabbers · Single or multi-channel MPEG-2 compression Video Controllers Analog VGA · TTL and DVI panels Communication Modules · Copper or fiber Ethernet USB 2.0 and Firewire · CAN Bus & CAN Spider · Dual Synchronous Serial Quad Serial w/ Ethernet Octal PCI Serial Wireless Telematics · GSM, GSM-R, CDMA EDGE, GPRS, SMS · GPS, Wi-Fi, Bluetooth **Motion Controllers**  DC motor controllers Synchro, resolver, LVDT

| Geode cpulviodules |                                         |                  |                  |                      |                      |                 | rentium in cpulviodules |                 |                 |                 |                 |                    |                 |                 |  |

|--------------------|-----------------------------------------|------------------|------------------|----------------------|----------------------|-----------------|-------------------------|-----------------|-----------------|-----------------|-----------------|--------------------|-----------------|-----------------|--|

|                    |                                         | Pentium® M       |                  |                      |                      | Intel® Celeron® |                         |                 |                 |                 |                 | AMD Geode          |                 |                 |  |

|                    | cpuModules <sup>™</sup><br>-40 to +85°C | CMX58886PX1400HR | CMD58886PX1400HR | CMX58886PX1400HR-BRG | CMD58886PX1400HR-BRG | CME47786CX650HR | CME47786HX650HR         | CML47786CX650HR | CML47786HX650HR | CMX47786CX650HR | CMX47786HX650HR | CME26686HX333HR    | CME27686HX333HR | CME27686CX333HR |  |

|                    | AT Expansion Bus                        |                  |                  | ~                    | ~                    | 1               | 1                       | Y               | Y               | ~               | ~               | 1                  | 1               | 1               |  |

| Bus                | <b>PCI Universal Expansion Bus</b>      | 1                | 1                | 4                    | 1                    | 1               | 1                       | 4               | 1               | 4               | 1               |                    | 1               | 1               |  |

| B                  |                                         | 4                | 4                | 4                    | 4                    | - 4             | 4                       | 4               | - 4             | 4               | 4               |                    | 4               | 4               |  |

|                    | APIC (add'l PCI interrupts)             | 9                | 9                | 9                    | 9                    | 9               | 9                       | 9               | 9               | 9               | 9               |                    |                 |                 |  |

|                    | CPU Max Clock Rate (MHz)                | 1400             | 1400             | 1400                 | 1400                 | 650             | 650                     | 650             | 650             | 650             | 650             | 333                | 333             | 333             |  |

|                    | L2 Cache                                | 2MB              | 2MB              | 2MB                  | 2MB                  | 256k            | 256k                    | 256k            | 256k            | 256k            | 256k            | 16K                | 16k             | 16k             |  |

| So                 | Intel SpeedStep Technology              | 1                | 1                | 1                    | 1                    |                 |                         |                 |                 |                 |                 |                    |                 |                 |  |

| 8                  | ACPI Power Mgmt                         | 2.0              | 2.0              | 2.0                  | 2.0                  | 1.0             | 1.0                     | 1.0             | 1.0             | 1.0             | 1.0             |                    |                 |                 |  |

| pur                | Max Onboard DRAM (MB)                   | 512              | 512              | 512                  | 512                  | 512             | 512                     | 512             | 512             | 512             | 512             | 256                | 256             | 256             |  |

| CPUa               | RTD Enhanced Flash BIOS                 | ~                | 1                | 1                    | 1                    | 1               | 1                       | 1               | 1               | 1               | 1               | 1                  | 1               | 1               |  |

|                    | Nonvolatile Configuration               | 1                | 1                | V                    | 1                    | 1               | ~                       | 1               | 1               | 1               | 1               | 1                  | 1               | 4               |  |

|                    | Quick Boot Option Installed             | 1                | 1                | 1                    | 1                    | 1               | 1                       | 1               | 1               | 1               | 1               | 1                  | 1               | 1               |  |

|                    | USB Boot                                | 1                | 1                | 1                    | 1                    | 1               | 1                       | 1               | 1               | 1               | 1               |                    |                 |                 |  |

| 7                  | Watchdog Timer & RTC                    | 1                | 1                | V                    | V                    | 1               | 1                       | 1               | 1               | 1               | 1               | 1                  | 1               | V               |  |

|                    | IDE and Floppy Controllers              | 1                | 1                | V                    | 1                    | 1               | 1                       | 1               | 1               | V               | 1               | 1                  | 1               | 1               |  |

|                    | SSD Socket, 32 DIP                      |                  |                  |                      |                      |                 | 1                       |                 | 1               |                 | 1               | 1                  | 1               |                 |  |